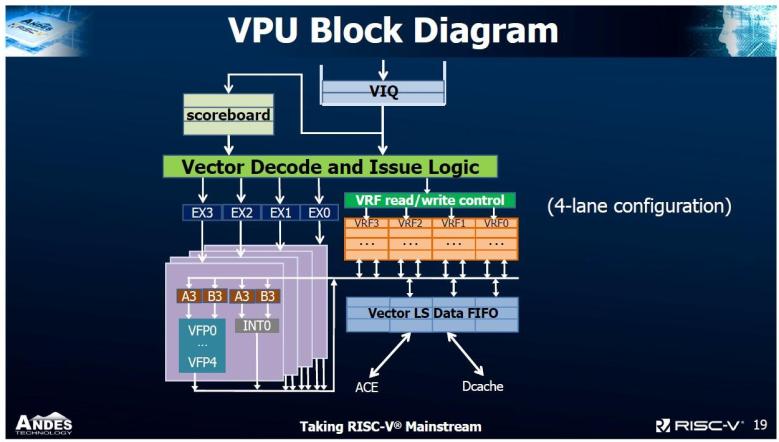

First Core with RISC-V Vector Instruction Extension Delivered

Andes’ new processor cores enable scalability by delivering RVV instruction extension and new memory subsystem. The company claims to be…

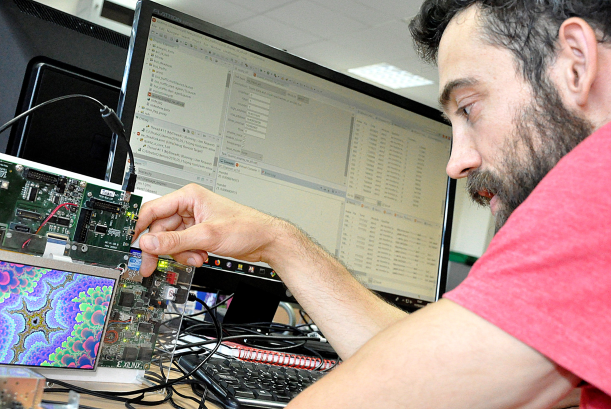

UltraSoC Donates Trace Encoder

Having the encoder available should help minimize the possible risk for potential RISC-V developers.

Arm Offer Response to RISC-V

After decades, Arm has finally decided to allow licensees to build their own custom instructions, which are often useful to…

Can Carbon Nanotubes Take Us Beyond Silicon?

MIT's work on carbon nanotube field-effect transistors validates a promising path towards practical beyond-silicon electronic systems.

Arm Launches New Service to Combat Open-Source Alternatives

Arm has made it easier for chip designers to experiment with its IP, with a flexible access engagement model that…

Embedded Benchmark Needs Support

A handful of mainly academic researchers aim to create EmBench, a free benchmark for embedded processors based on real-world applications

Qualcomm is the Newest Investor in SiFive

RISC-V is heading for mobile. Qualcomm participated in SiFive's $65.4m funding round. We talked CEO Naveed Sherwani recently about the…

MIPS Open R6 Architecture Now Available

MIPS 32-bit and 64-bit architecture – the most recent version, release 6 – became available Thursday (March 28) for anyone…

Intel, RISC-V Groups Race to Develop Tomorrow’s Processors

Intel and RISC-V backers announced rival alliances to nurture competing ecosystems around tomorrow’s processors.

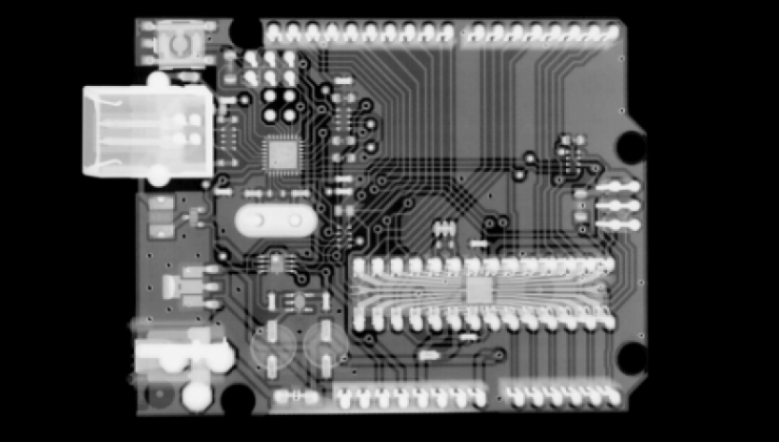

On-Chip Analytics to ‘See’ into Complex ML, AI Chips

Heterogeneous multicore chips are becoming increasingly common, particularly in enabling the ML and AI technologies required in leading-edge applications such…