Resolve process variation challenges in multiple patterning

Article By : Richard A. Gottscho

Multiple patterning is an effective method for pitch shrinking now standard in high-volume production. However, as the number of process steps increases, managing variation becomes a challenge.

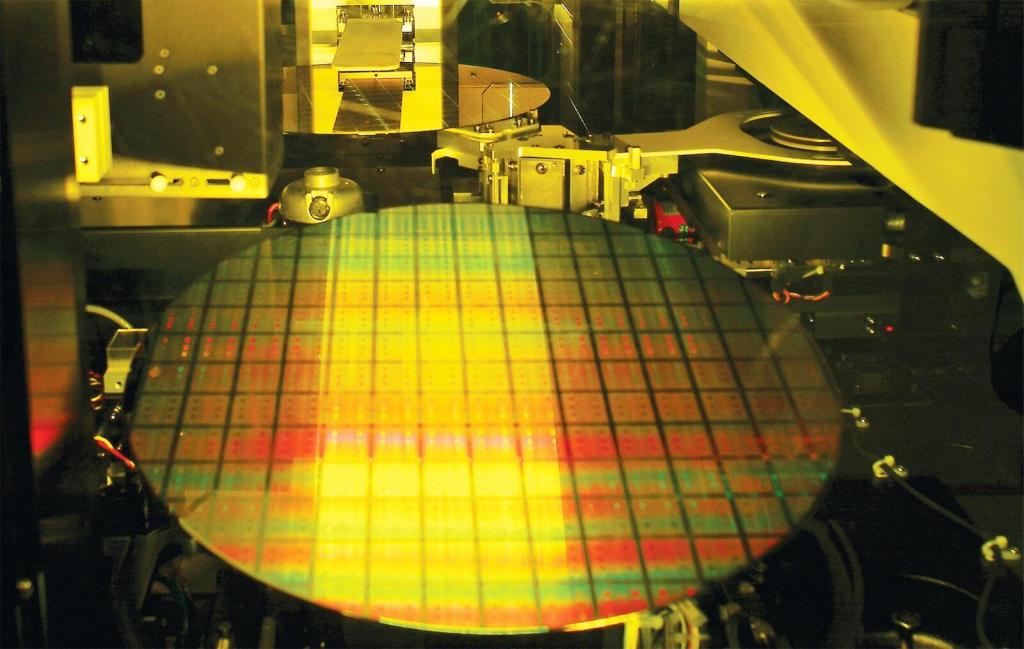

Multiple patterning, a method for increasing IC feature density beyond the limits of conventional lithography capability, has emerged as an important technology for manufacturing advanced chips (see Enabling advanced ICs with multiple patterning). This technique has proven to be an effective method for pitch shrinking with two- and four-fold reductions now standard in high-volume production. However, as the number of process steps increases, managing variation becomes more critical.

For example, in the self-aligned quadruple patterning approach, critical dimension (CD) is impacted by lithography, deposition, etch and clean, potentially resulting in three different contributions to CD variation of the space between lines. Stringent control is required at each process step of the multiple patterning scheme to ensure consistent line placement required for device scaling.

CD uniformity

The maximum allowable variation in patterning is quantified as “edge placement error.” Generally, this should be less than 30% of the minimum feature pitch and includes all sources of variation. To meet this requirement at the 5nm node, variation across the wafer must be less than 0.5nm.

Control of plasma etch across the wafer is critical to the overall chain of process uniformity management efforts. Key challenges include managing inherent thermal, chemical and electrical discontinuities due to the finite wafer size, as well as developing tuning methods that can provide independent control of process parameters.

Initial innovations to reduce variability focused primarily on tuning the plasma chemistry across the wafer, such as injecting reactant gases from multiple locations and adding tuning gases in specific areas to control the reactant ratio at the wafer edge versus the center. This enabled a significant step forward in controlling the chemistry and convective transport factors that impact variability. Process control methods evolved with multiple injection locations—including at the wafer edge—to significantly improve the spatial resolution of chemistry control.

Temperature control

Another key advance in managing variability has been development of tunable temperature control. Etching offers an opportunity to correct for incoming variation by deliberately creating a high spatial resolution, non-uniform temperature profile. Changing the wafer temperature locally affects the probability of whether passivants will stick to the sidewalls of the etched feature. For example, lower temperatures lead to more sidewall passivation and larger line CDs. If smaller line CDs are desired, manufacturers correspondingly increase the temperature. By pre-measuring CDs coming into the system and feeding that information forward to the temperature controllers, temperature can then be used to compensate for incoming CD variability and minimise within-wafer CD variation, reducing CD non-uniformity after etch by as much as three-fold.

Atomic-layer processing

Device feature sizes are continuing to shrink and are now approaching the atomic level. Therefore, to continue controlling variability, atomic-layer processes are being used. Atomic-layer deposition (ALD) creates films just a few atomic layers at a time and atomic-layer etching (ALE) removes material in the same manner. Since spacer thickness control is crucial to determining CD in self-aligned multiple patterning, ALD is used to produce highly conformal and uniform spacers. Similarly, ALE can be used to reduce or eliminate dependency of profile, CD and etch depth on feature size and pattern loading.

While these multiple patterning processes have proven to help reduce variability and enable continued scaling, the additional steps increase manufacturing costs and uniformity control at the wafer’s edge remains a concern. Continued collaboration between equipment makers and chip manufacturers is needed to overcome these challenges and further the use of multiple patterning for creating the next generation of chips.

Reference:

Mulkens, Jan (2017). Patterning control strategies for minimum edge placement error in logic devices, SPIE, San Jose, CA, February 2017.

Richard Gottscho, Ph.D., is executive VP, Global Products at Lam Research Corp.

« Previously: Enabling advanced ICs with multiple patterning