Ceva Pitches New DSP Core

Article By : Junko Yoshida

For telecom equipment vendors, designing the right 5G network gear is a moving target. Ceva unveiled its newest DSP architecture, and the multicore CEVA-XC 16, the first processor in the family.

PARIS — For telecom equipment vendors, designing the right 5G network gear is a moving target that keeps going higher. As 5G advances from the current New Radio (NR) Phase I to Phase II, the new 5G Radio Access Network demands more transport flexibility and different base station functional splits.

With that in mind, Ceva, a licensor of DSP cores, unveiled Wednesday its newest DSP architecture, called the Gen4 CEVA-XC.

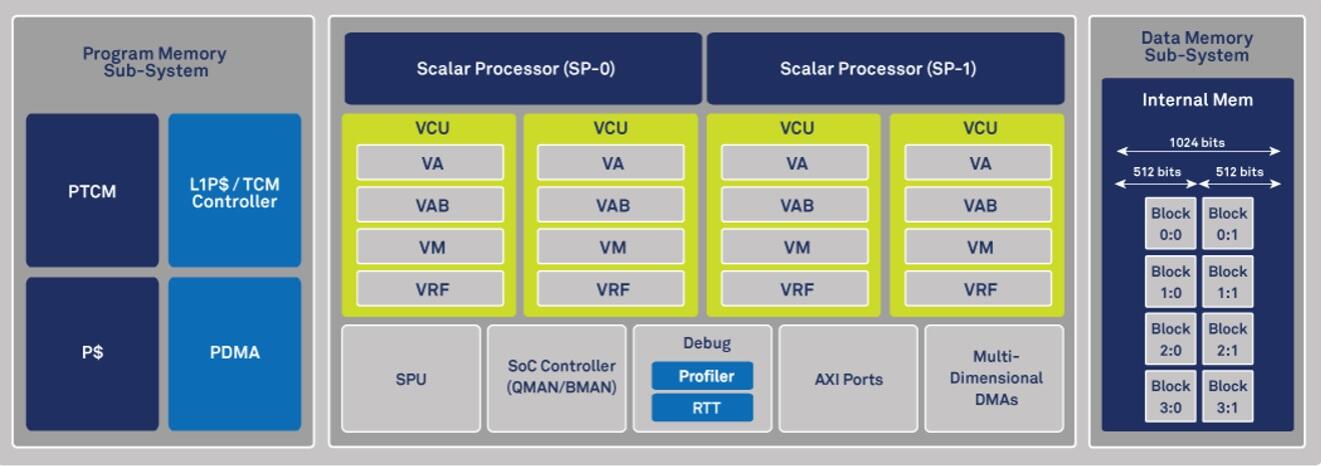

The Gen4 CEVA-XC is “much more than a DSP core,” according to Nir Shapira, business development director, mobile broadband business unit at Ceva. Describing it as “more of a complete compute platform,” he said the new DSP core natively features multithread and multicore architecture. It contains a built-in scheme designed for dynamic-vector computing resource allocation.

With the enhanced micro-architecture, its clock speed reaches 1.8 GHz at 7nm process node. The Gen4 CEVA-XC claims to offer 1.5 times performance/area, compared to the company’s previous DSP core architecture. The ability to squeeze more processing power into a smaller space is great news for network equipment designers. It means they don’t need to add more DSP cores to beef up 5G SoC performance, which must meet the demands of the new 5G Radio Access Networks (RAN).

This is “the best vector DSP out there,” claimed Shapira.

Along with the new Gen4 CEVA-XC launch, Ceva also announced the multicore CEVA-XC 16, the first processor in the family based on the new architecture.

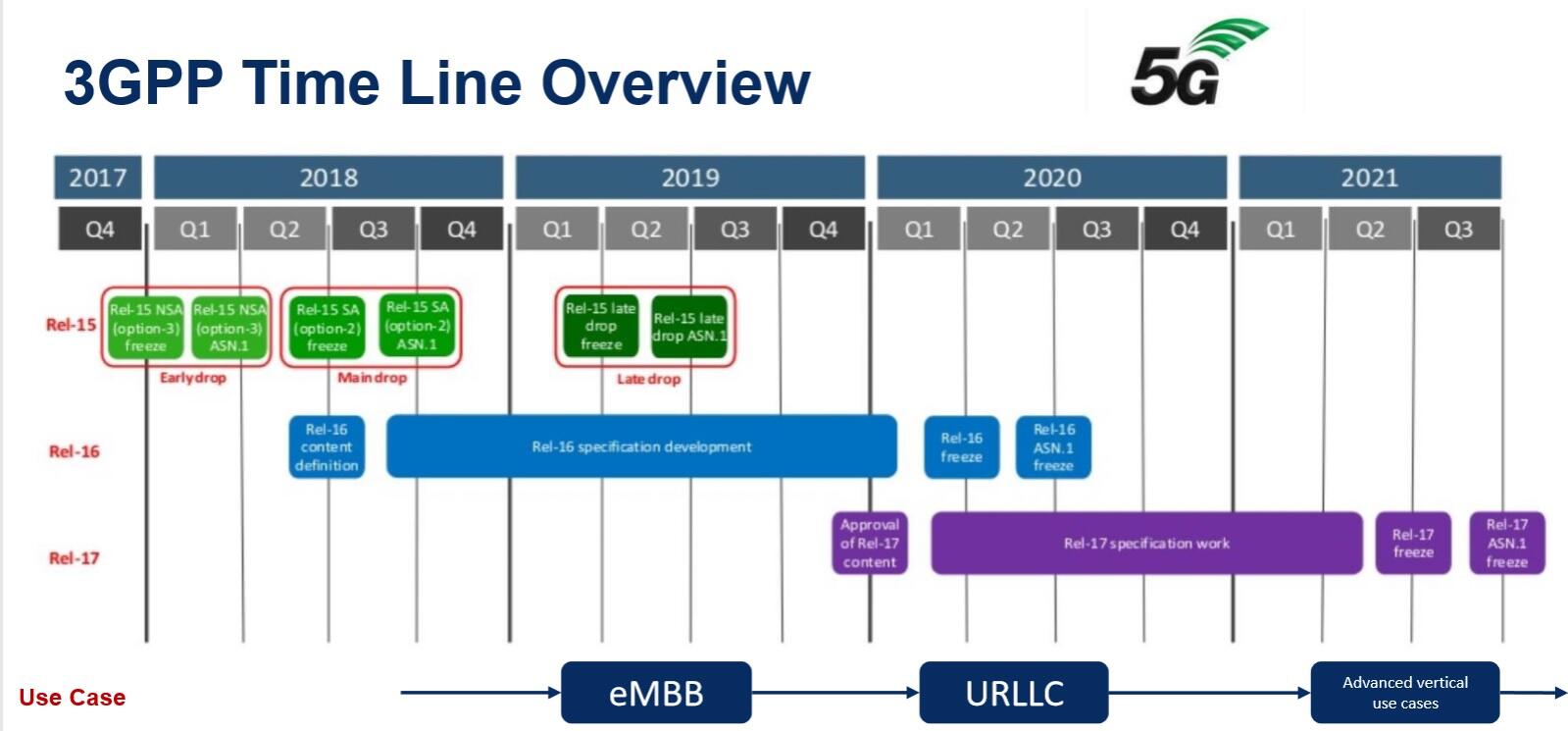

The rollout of the XC16 comes as the deployment of 5G NR Phase II is on the horizon. The 5G RAN currently on the network is based on 3GPP’s 5G Release 15 (Rel-15) specifications. But the mobile network is poised to move on to 5G NR Phase II based on Rel-16 and Rel-17 specs.

5G NR Phase I vs. Phase 2

Mike Demler, senior analyst at The Linley Group, said that the thing to remember about 5G is that “it is going to be a long multiyear rollout, as the Rel-15, -16, -17 timeline shows.”

He cautioned, “All the early 5G hype needs to be tempered by that reality.”

Demler noted, “Because of Ceva’s customer base, they tend to be on the leading edge for whatever 3GPP is currently working on. Customers often start building before the specs are ratified, but not before they’re well into the approval stage. So that requires continuous improvement as you see in Ceva’s XC12 to XC16.”

5G NR Phase I is implemented in the current 5G network. It requires “enhanced Mobile Broadband,” as defined by the 3GPP Rel-15 spec. Its required features include Gigabit throughput, Massive MIMO, Massive Carrier Aggregation, Fixed Wireless Access mmWave and heterogeneous network orchestration, under which multiple types of access nodes populate a wireless network.

In contrast, the soon-to-emerge 5G NR Phase II offers features like “Ultra Reliable Low Latency Communications” and “massive Machine Type Communications,” defined by 3GPP’s Rel-16 and Rel-17.

More specifically, ultra-reliable low latency communication advances the possibilities for “remote surgery,” for example, or mission-critical “AR/VR,” gaming applications, or cellular-based vehicle-to-everything automotive communication over the 5G network, explained Moshe Sheier, vice president of marketing at Ceva.

This means that sub-1ms latency must be enabled in the 5G RAN, while for some applications the base band unit must be much closer to users — sometimes in a cabinet in a room.

In short, new 5G applications demand a lot of rethinking on 5G networks. Network operators may need to consider the functional split used for RAN and Cloud-RAN deployments, for example.

As a result, the new 5G networks in Phase II are expected to handle many more modes and architectures, providing 5G network equipment greater flexibility while offering massive processing capabilities, explained Shapira.

What’s significant about Gen4 CEVA-XC DSP?

Demler called the Gen4 CEVA-XC DSP “mostly evolutionary” like every generation of CEVA DSP, as seen in ì2x increase in MAC units per core for each generation.

However, he noted, “The most significant architectural upgrade is the dynamic multithread capability. All their previous DSPs had one scalar unit and multiple vector units. The new configuration with two scalars offers a great degree of flexibility, and on-the-fly configurability.”

Ceva’s Shapira added that another highlight is a unique memory subsystem introduced to the Gen4 CEVA-XC DSP architecture. The subsystem, tightly coupled with memory, supports simultaneous multi-threading and memory access.

Why dynamic multicore is important

The new 5G RAN demands dynamic support for “mass multi-user” and “large single user” allocations. That’s where multithread and multicore come in. Shapira explained, more in detail, how the dynamic multicore works:

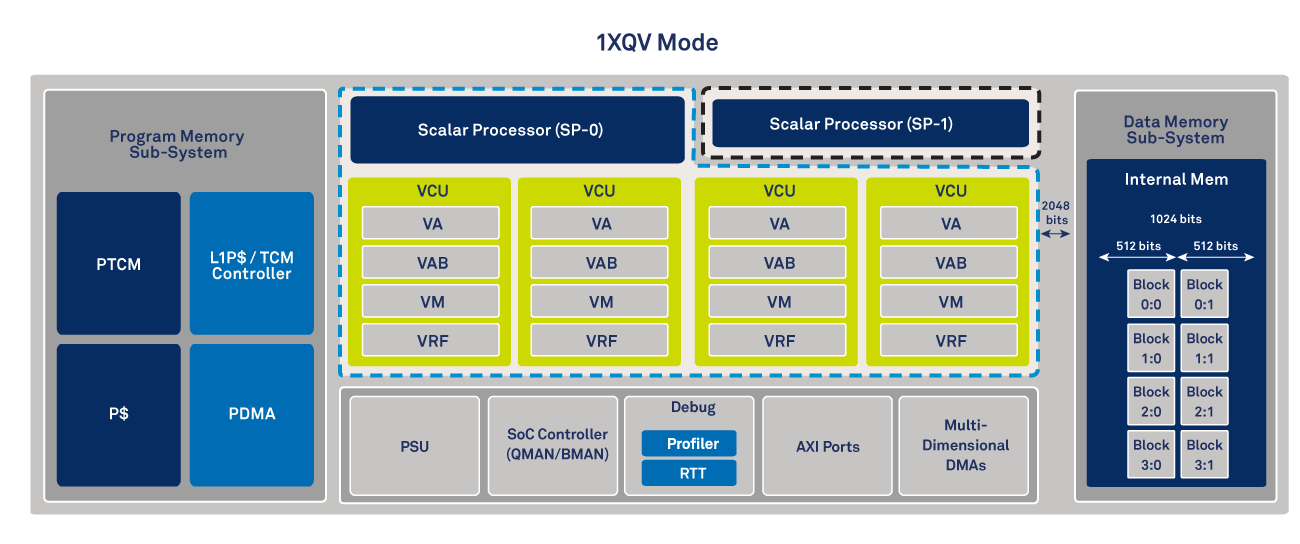

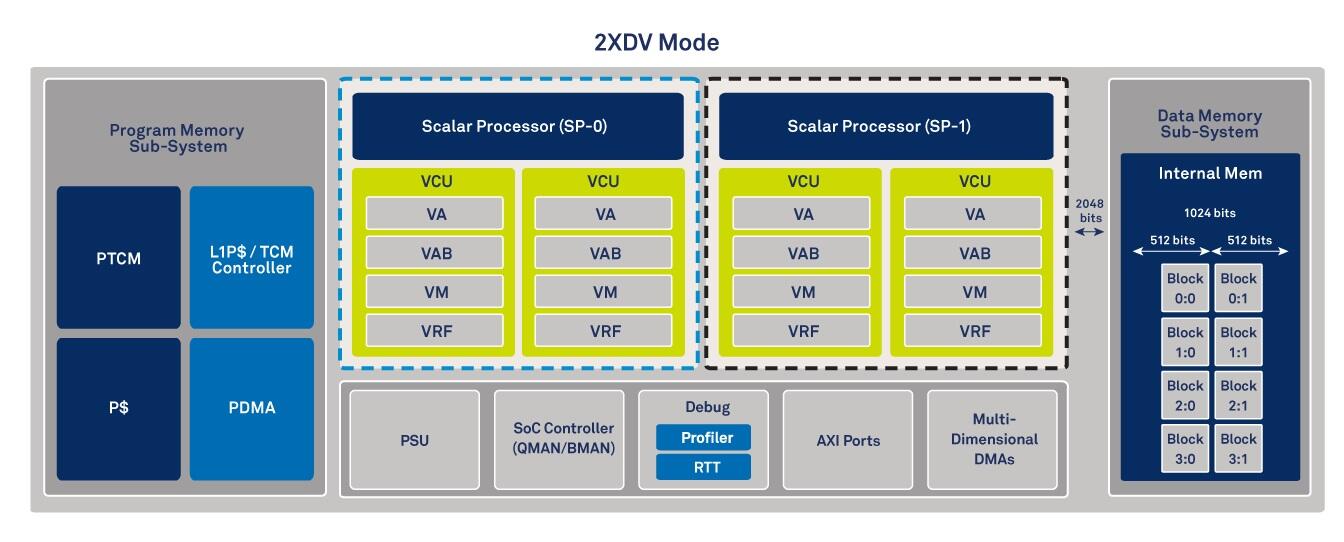

The new DSP architecture, for example, allows all Vector Computation Units (VCU) assigned to Scaler Processor 0. Meanwhile Scaler Processor 1 can run in parallel as a controller. He calls it Mode 1: 1xQV (Quad Vector). In contrast, the new DSP can also assign Scaler Processor 0 and 1 as two Vector Computation Units each. He calls it Mode 2: 2X DV (Dual Vector). Under this mode, symmetric processing flows.

The value of the architecture is that mode changes can be enacted dynamically, and can be switched in “a few cycles,” he added.

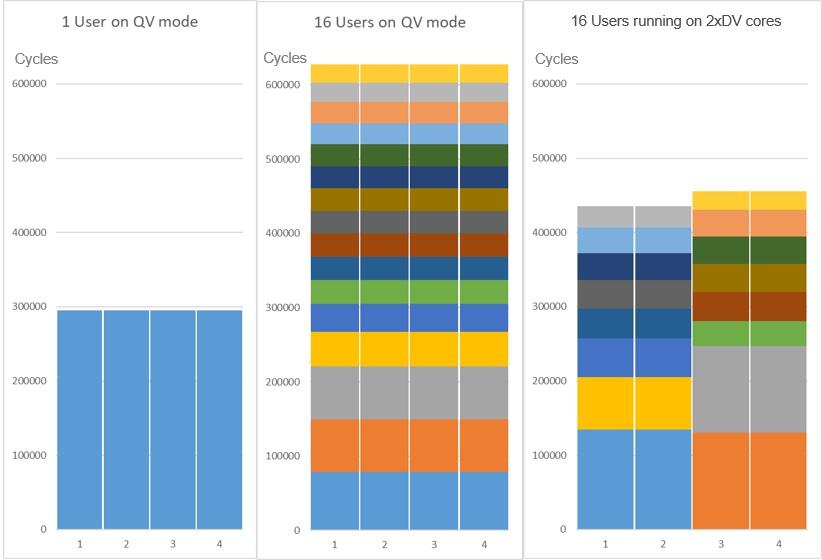

QV vs. DV X2 dynamic multithread becomes particularly important in channel estimation tasks in 5G. Take the example of 5G NR 4×4 channel estimation. The whole channel in QV mode can be used by one user.

On the other hand, 16 users can also share the same channel in the QV mode. However, with that many users, control overhead doubles the overall cycle load and it doesn’t prove to be an efficient way of sharing the channel.

But by switching to dual thread mode (DV X2), there is significant improvement for multiple users, explained Ceva, as one can see in the diagram below.

Competition

Because of the evolutionary nature of the 5G network, telecom gear developers like Nokia tend to depend on more programmable solutions. Ceva’s Shapira said, “Nokia initially deployed an FPGA-based platform for 5G.”

But as 5G deployment ramps up, network equipment vendors are seeking more power-efficient solutions for their 5G chips, he noted.

Marvell just upgraded its telecom infrastructure processor called Octeon. Calling Octeon basically an ASIC, Shapira observed that, as the 5G spec evolves to Rel-16 and Rel-17, “Many more new flavors of 5G will be coming in. Vendors will look for a way to add more flexibility.”

Asked about Ceva’s competition in the IP core market, Demler noted that last year, Cadence rolled out its ConnX B20 to address some of the same [5G] applications Ceva is referring to. He added, “But the Tensilica DSPs are more a collection of configurable components than a complete pre-packaged solution like Ceva’s XC16.” Ceva’s Sheier, however, made it clear, “While XC16 is a dedicated 5G platform, Tensilica provides general purpose DSPs that cannot address 5G infrastructure needs.”

In Demler’s opinion, “As far as competition goes, there’s not much else in licensable DSP IP besides Tensilica. The greatest competition will come from in-house designs.”